# Ultralow Noise VGAs with Preamplifier and Programmable $R_{\text{IN}}$

# AD8331/AD8332/AD8334

#### **FEATURES**

Ultralow noise preamplifier (preamp) Voltage noise = 0.74 nV/√Hz

Current noise = 2.5 pA/√Hz

3 dB bandwidth

AD8331: 120 MHz

AD8332, AD8334: 100 MHz

Low power

AD8331: 125 mW/channel

AD8332, AD8334: 145 mW/channel

Wide gain range with programmable postamp

-4.5 dB to +43.5 dB in LO gain mode

+7.5 dB to +55.5 dB in HI gain mode

Low output-referred noise: 48 nV/√Hz typical

**Active input impedance matching**

Optimized for 10-bit/12-bit ADCs

Selectable output clamping level

Single 5 V supply operation

AD8332 and AD8334 available in lead frame chip scale package

#### **APPLICATIONS**

Ultrasound and sonar time-gain controls

High performance automatic gain control (AGC) systems

I/Q signal processing

High speed, dual ADC drivers

#### **GENERAL DESCRIPTION**

The AD8331/AD8332/AD8334 are single-, dual-, and quadchannel, ultralow noise linear-in-dB, variable gain amplifiers (VGAs). Optimized for ultrasound systems, they are usable as a low noise variable gain element at frequencies up to 120 MHz.

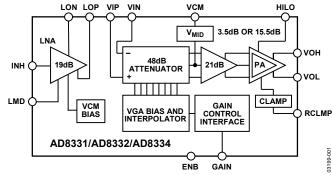

Included in each channel are an ultralow noise preamp (LNA), an X-AMP\* VGA with 48 dB of gain range, and a selectable gain postamp with adjustable output limiting. The LNA gain is 19 dB with a single-ended input and differential outputs. Using a single resistor, the LNA input impedance can be adjusted to match a signal source without compromising noise performance.

The 48 dB gain range of the VGA makes these devices suitable for a variety of applications. Excellent bandwidth uniformity is maintained across the entire range. The gain control interface provides precise linear-in-dB scaling of 50 dB/V for control voltages between 40 mV and 1 V. Factory trim ensures excellent part-to-part and channel-to-channel gain matching.

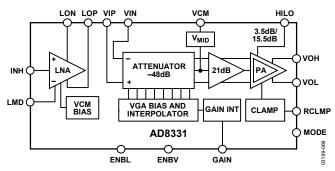

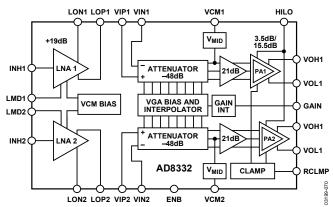

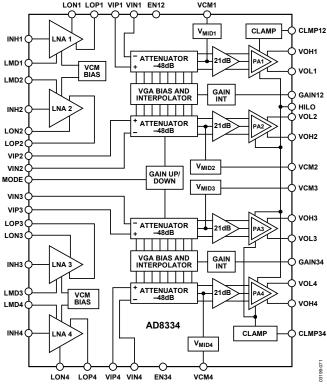

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Signal Path Block Diagram

Figure 2. Frequency Response vs. Gain

Differential signal paths result in superb second- and thirdorder distortion performance and low crosstalk.

The low output-referred noise of the VGA is advantageous in driving high speed differential ADCs. The gain of the postamp can be pin selected to 3.5 dB or 15.5 dB to optimize gain range and output noise for 12-bit or 10-bit converter applications. The output can be limited to a user-selected clamping level, pre-venting input overload to a subsequent ADC. An external resistor adjusts the clamping level.

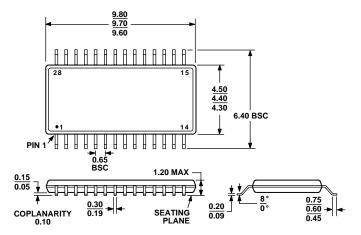

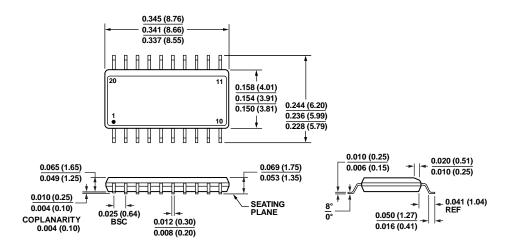

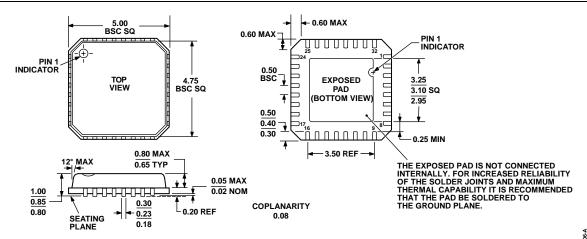

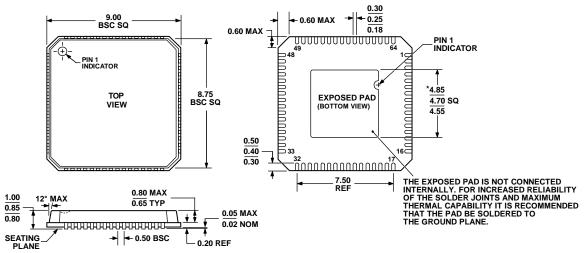

The operating temperature range is  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . The AD8331 is available in a 20-lead QSOP package, the AD8332 is available in 28-lead TSSOP and 32-lead LFCSP packages, and the AD8334 is available in a 64-lead LFCSP package.

# **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagram                     | 1  |

| Revision History                             | 3  |

| Specifications                               | 4  |

| Absolute Maximum Ratings                     | 7  |

| ESD Caution                                  | 7  |

| Pin Configurations and Function Descriptions | 8  |

| Typical Performance Characteristics          | 12 |

| Test Circuits                                | 20 |

| Measurement Considerations                   | 20 |

| Theory of Operation                          | 24 |

| Overview                                     | 24 |

| Low Noise Amplifier (LNA)                    | 25 |

| Variable Gain Amplifier                      | 27 |

| Postamplifier                                | 28 |

| Applications Information                     | 30 |

| LNA—External Components                      | 30 |

| Driving ADCs                                 | 32 |

| Overload                                     | 32 |

| Optional Input Overload Protection           | 32 |

| Layout, Grounding, and Bypassing             | 33 |

| Multiple Input Matching                      | 33 |

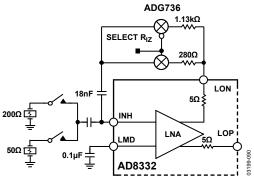

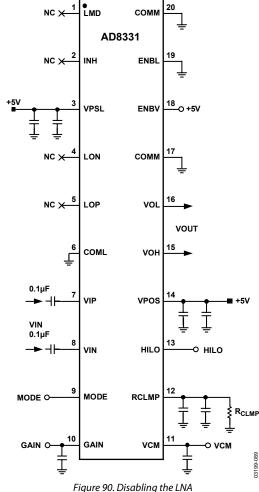

| Disabling the LNA                            | 33 |

| Ultrasound TGC Application                   | 34 |

| High Density Ouad Layout                     | 34 |

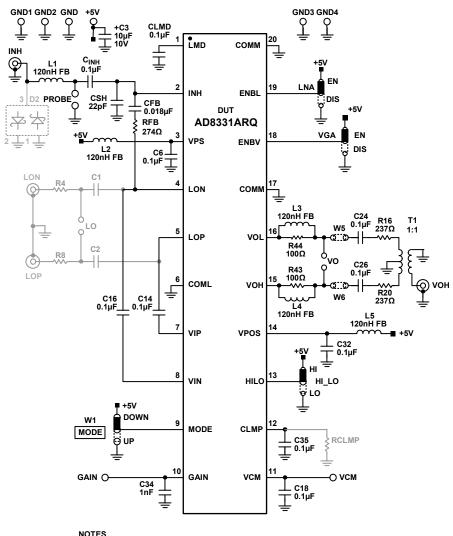

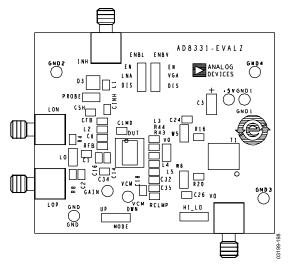

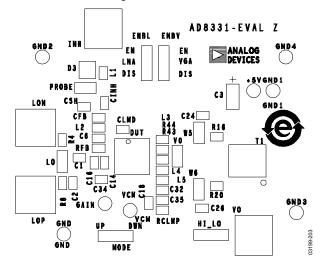

| AD8331 Evaluation board              |

|--------------------------------------|

| General Description                  |

| User-Supplied Optional Components    |

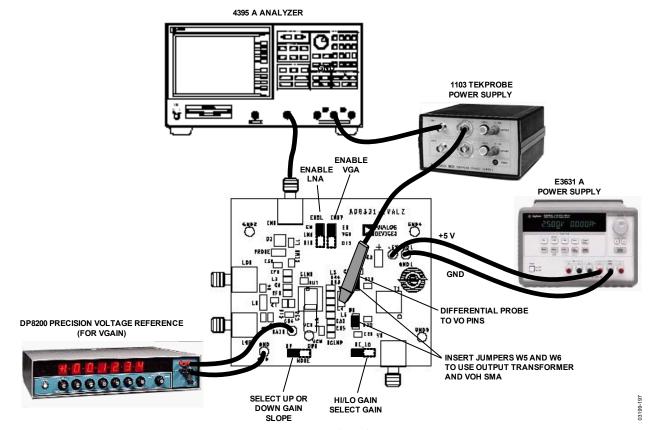

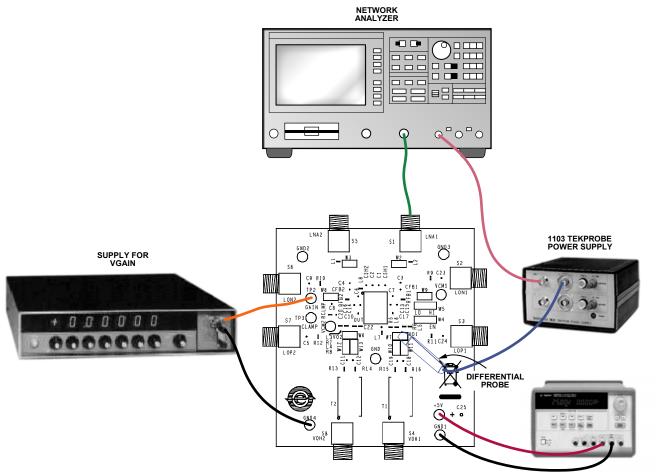

| Measurement Setup                    |

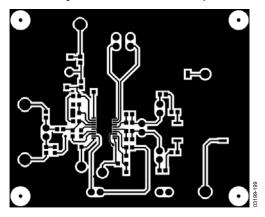

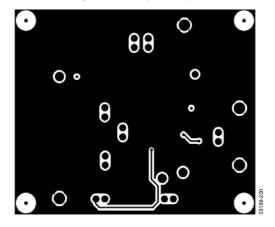

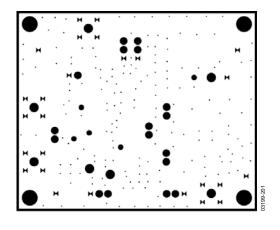

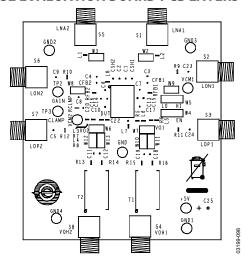

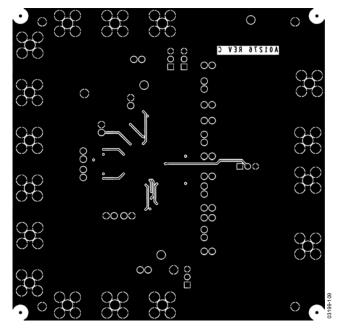

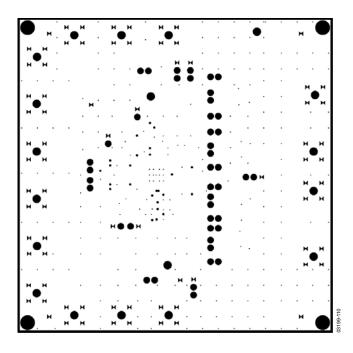

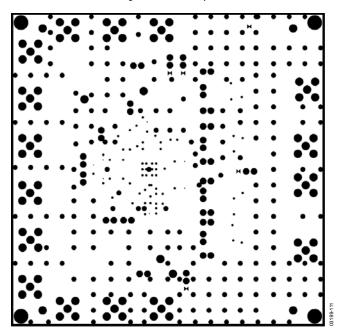

| Board Layout                         |

| AD8331 Evaluation Board Schematics   |

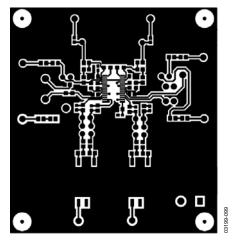

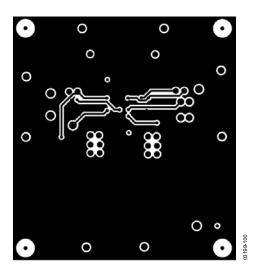

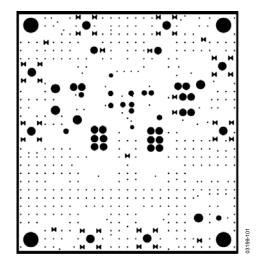

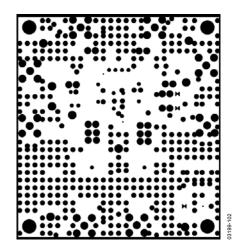

| AD8331 Evaluation Board PCB Layers   |

| AD8331 Bill of Materials43           |

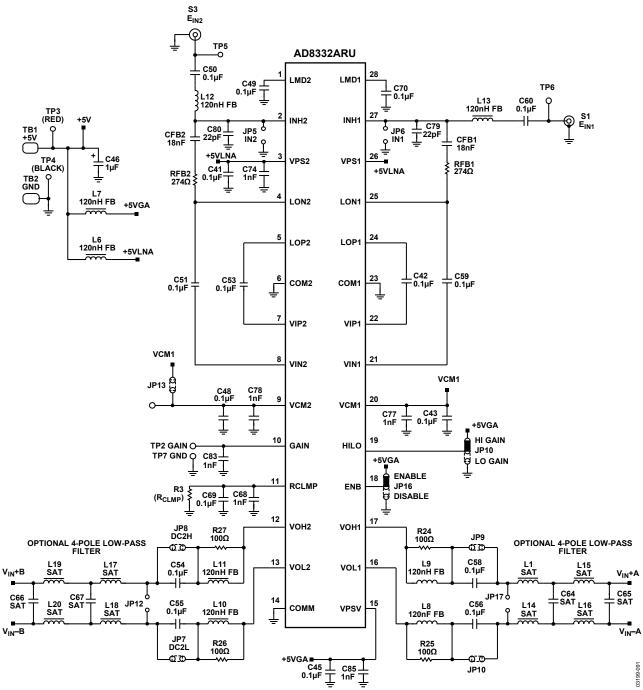

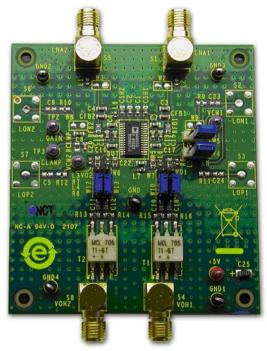

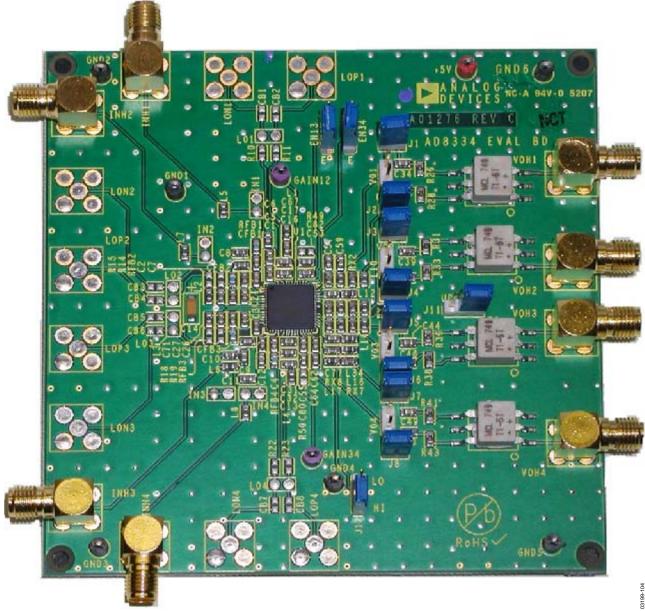

| AD8332 Evaluation Board              |

| General Description                  |

| User-Supplied Optional Components44  |

| Measurement Setup44                  |

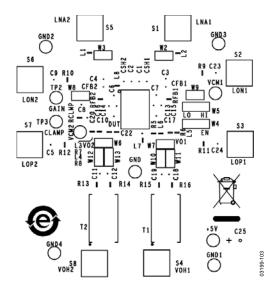

| Board Layout                         |

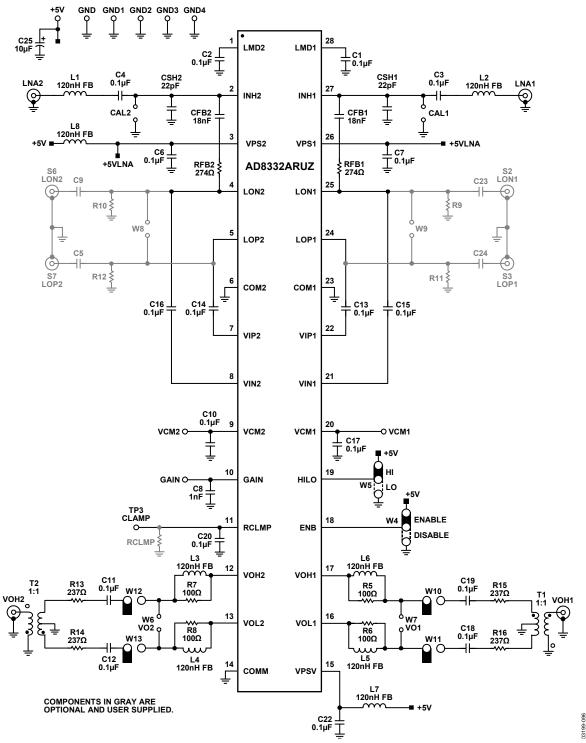

| Evaluation Board Schematics          |

| AD8332 Evaluation Board PCB Layers47 |

| AD8332 Bill of Materials48           |

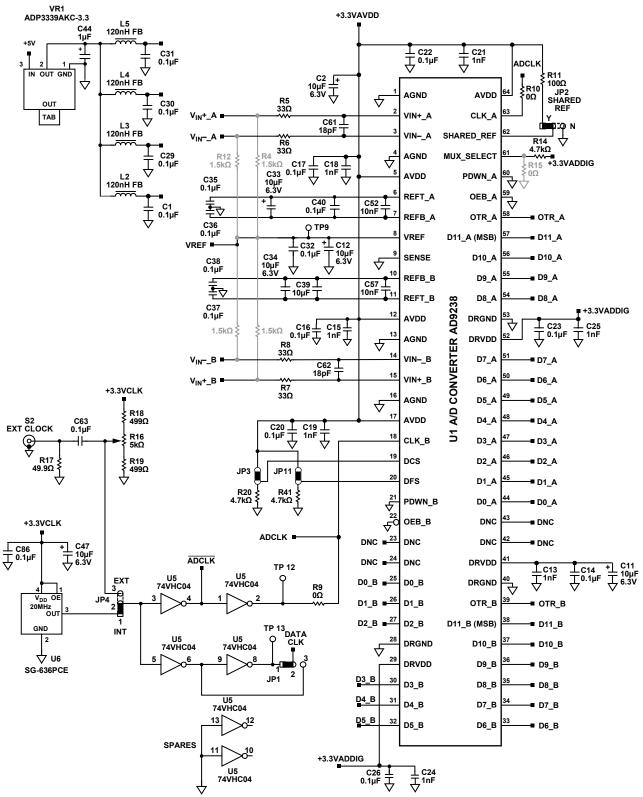

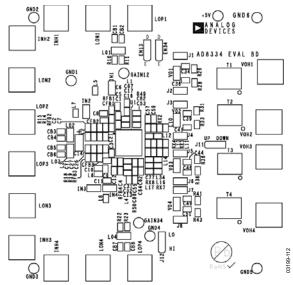

| AD8334 Evaluation Board              |

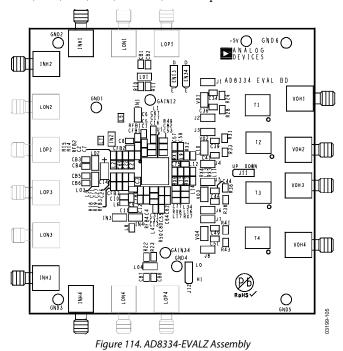

| General Description                  |

| Configuring the Input Impedance      |

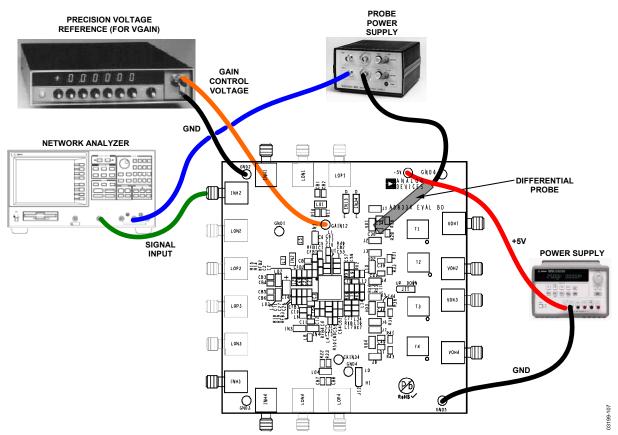

| Measurement Setup50                  |

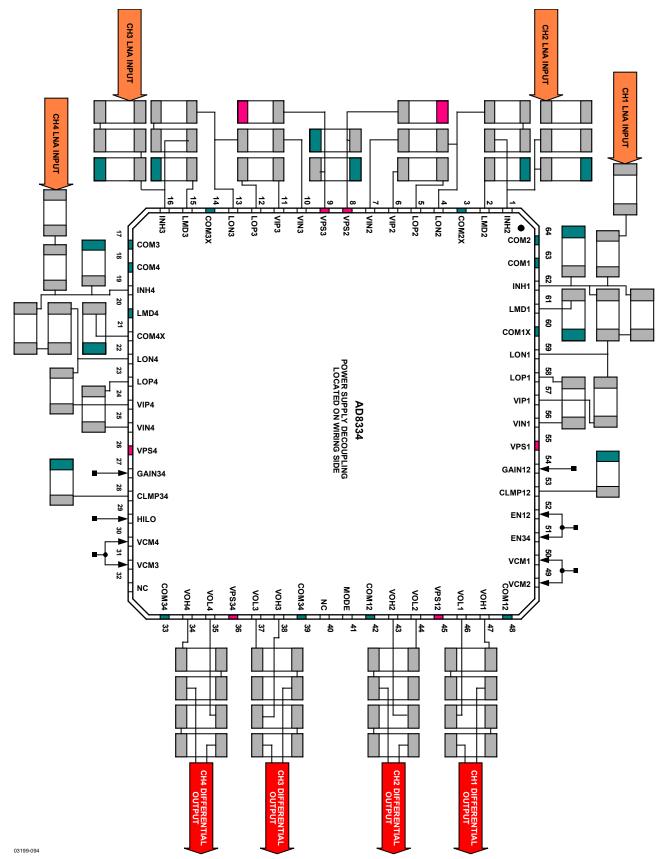

| Board Layout50                       |

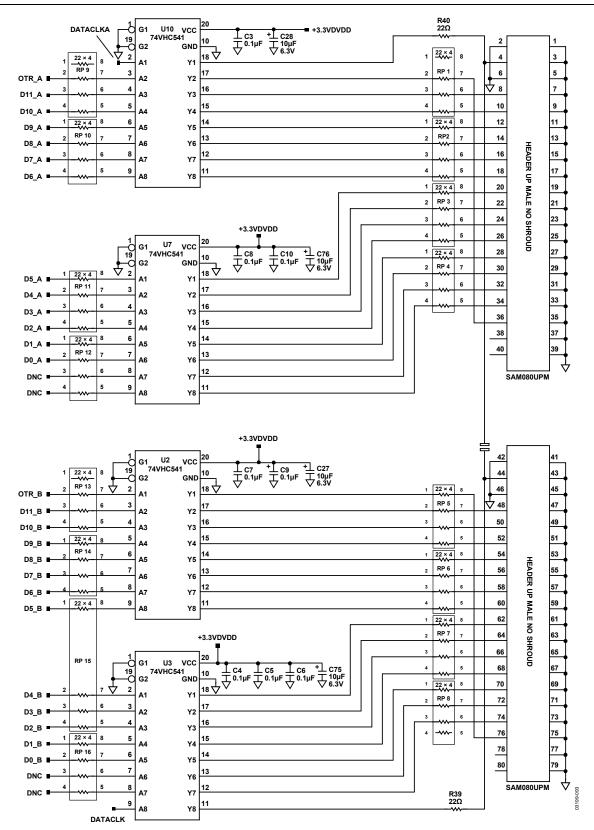

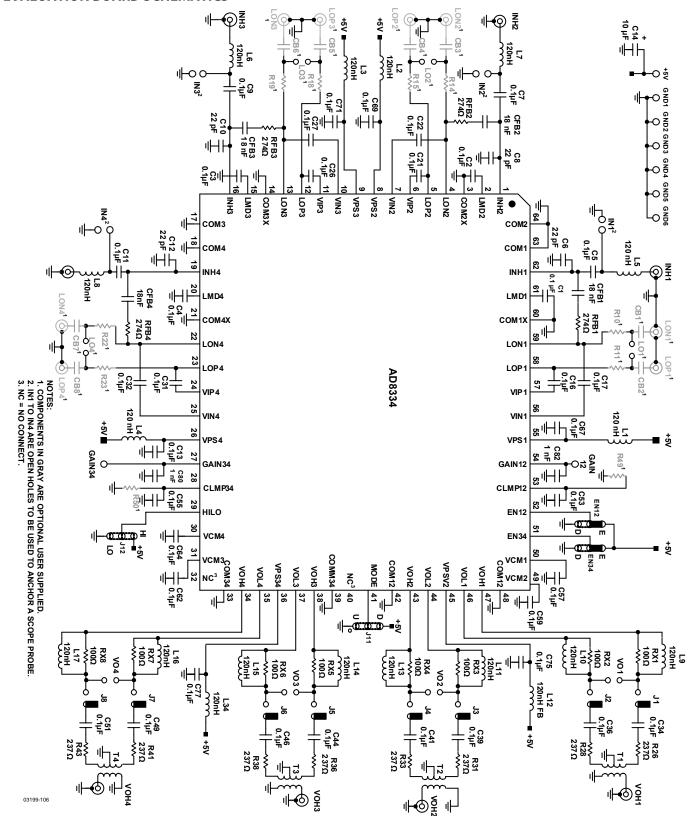

| Evaluation Board Schematics51        |

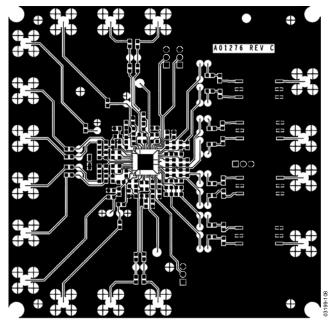

| AD8334 Evaluation Board PCB Layers53 |

| AD8334 Bill of Materials54           |

| Outline Dimensions                   |

| Ordering Guide57                     |

### **REVISION HISTORY**

| 4/08—Rev. E to Rev. F                                      |       |

|------------------------------------------------------------|-------|

| Changed R <sub>FB</sub> to R <sub>IZ</sub> Throughout      | 4     |

| Changes to Figure 1                                        | 1     |

| Changes to Table 1, LNA and VGA Characteristics, Output    |       |

| Offset Voltage, Conditions                                 | 4     |

| Changes to Quiescent Current per Channel and Power Dow     |       |

| Current Parameters                                         |       |

| Changes to Table 2                                         | 7     |

| Changes to Table 3, Pin 1 Description                      | 8     |

| Changes to Table 4, Pin 1 and Pin 28 Descriptions          |       |

| Changes to Table 5, Pin 4 and Pin 5 Descriptions           | 9     |

| Changes to Table 6, Pin 2, Pin 15, and Pin 20 Descriptions |       |

| Changes to Table 6, Pin 61 Description                     | 11    |

| Changes to Typical Performance Characteristics Section,    |       |

| Default Conditions                                         | 12    |

| Changes to Figure 25                                       | 15    |

| Changes to Figure 39                                       | 17    |

| Changes to Figure 55 Through Figure 68                     | 20    |

| Changes to Theory of Operation, Overview Section           | 24    |

| Changes to Low Noise Amplifier Section and Figure 74       | 25    |

| Changes to Active Impedance Matching Section, Figure 75,   |       |

| and Figure 77                                              | 26    |

| Changes to Figure 78                                       | 27    |

| Changes to Equation 6, Table 7, Figure 81, and Figure 82   | 30    |

| Changes to Figure 83                                       | 31    |

| Changes to Figure 88                                       | 32    |

| Switched Figure 89 and Figure 90                           | 33    |

| Changes to Figure 89                                       |       |

| Changes to Ultrasound TGC Application Section              |       |

| Incorporated AD8331-EVAL Data Sheet, Rev. A                |       |

| Changes to User-Supplied Optional Components Section       |       |

| and Measurement Setup Section                              |       |

| Changes to Figure 95                                       |       |

| Changes to Figure 97                                       |       |

| Added Figure 98                                            |       |

| Incorporated AD8332-EVALZ Data Sheet, Rev. D               |       |

| Incorporated AD8334-EVAL Data Sheet, Rev. 0                |       |

| Updated Outline Dimensions                                 |       |

| Changes to Ordering Guide                                  | 57    |

| 4/06—Rev. D to Rev. E                                      |       |

| Added AD8334Unive                                          | ersal |

| Changes to Figure 1 and Figure 2                           | 1     |

| Changes to Table 1                                         |       |

| Changes to Table 2                                         | 7     |

| Changes to Figure 7 through Figure 9 and Figure 12         | 12    |

| Changes to Figure 13, Figure 14, Figure 16, and Figure 18  | 13    |

|                                                            |       |

| Changes to Figure 23 and Figure 24                   | 14     |

|------------------------------------------------------|--------|

| Changes to Figure 25 through Figure 27               |        |

| Changes to Figure 31 and Figure 33 through Figure 36 |        |

| Changes to Figure 37 through Figure 42               |        |

| Changes to Figure 43, Figure 44, and Figure 48       |        |

| Changes to Figure 49, Figure 50, and Figure 54       |        |

| Inserted Figure 56 and Figure 57                     |        |

| Inserted Figure 58, Figure 59, and Figure 61         |        |

| Changes to Figure 60                                 |        |

| Inserted Figure 63 and Figure 65                     | 22     |

| Changes to Figure 64                                 | 22     |

| Moved Measurement Considerations Section             | 23     |

| Inserted Figure 67 and Figure 68                     | 23     |

| Inserted Figure 70 and Figure 71                     | 24     |

| Change to Figure 72                                  |        |

| Changes to Figure 73 and Low Noise Amplifier Section | 25     |

| Changes to Postamplifier Section                     | 28     |

| Changes to Figure 80                                 | 29     |

| Changes to LNA—External Components Section           | 30     |

| Changes to Logic Inputs—ENB, MODE, and HILO Section  | n31    |

| Changes to Output Decoupling and Overload Sections   | 32     |

| Changes to Layout, Grounding, and Bypassing Section  | 33     |

| Changes to Ultrasound TGC Application Section        | 34     |

| Added High Density Quad Layout Section               | 34     |

| Inserted Figure 94                                   | 38     |

| Updated Outline Dimensions                           | 39     |

| Changes to Ordering Guide                            | 40     |

| 3/06—Rev. C to Rev. D                                |        |

| Updated Format                                       | versal |

| Changes to Features and General Description          |        |

| Changes to Table 1                                   |        |

| Changes to Table 2                                   |        |

| Changes to Ordering Guide                            |        |

| 11/03—Rev. B to Rev. C                               |        |

| Addition of New Part                                 |        |

| Changes to Figures                                   |        |

| 6 6                                                  |        |

| Updated Outline Dimensions                           | 32     |

| 5/03—Rev. A to Rev. B                                |        |

| Edits to Ordering Guide                              |        |

| Edits to Ultrasound TGC Application Section          |        |

| Added Figure 71, Figure 72, and Figure 73            |        |

| Updated Outline Dimensions                           | 31     |

| 2/03—Rev. 0 to Rev. A                                |        |

| Edits to Ordering Guide                              | 32     |

# **SPECIFICATIONS**

$T_A = 25$ °C,  $V_S = 5$  V,  $R_L = 500$   $\Omega$ ,  $R_S = R_{IN} = 50$   $\Omega$ ,  $R_{IZ} = 280$   $\Omega$ ,  $C_{SH} = 22$  pF, f = 10 MHz,  $R_{CLMP} = \infty$ ,  $C_L = 1$  pF, VCM pin floating, -4.5 dB to +43.5 dB gain (HILO = LO), and differential output voltage, unless otherwise specified.

Table 1.

| Parameter                          | Conditions                                                                | Min Typ | Max | Unit <sup>1</sup> |

|------------------------------------|---------------------------------------------------------------------------|---------|-----|-------------------|

| LNA CHARACTERISTICS                |                                                                           |         |     |                   |

| Gain                               | Single-ended input to differential output                                 | 19      |     | dB                |

|                                    | Input to output (single-ended)                                            | 13      |     | dB                |

| Input Voltage Range                | AC-coupled                                                                | ±275    |     | mV                |

| Input Resistance                   | $R_{IZ} = 280 \Omega$                                                     | 50      |     | Ω                 |

|                                    | $R_{IZ} = 412 \Omega$                                                     | 75      |     | Ω                 |

|                                    | $R_{IZ} = 562 \Omega$                                                     | 100     |     | Ω                 |

|                                    | $R_{IZ} = 1.13 \text{ k}\Omega$                                           | 200     |     | Ω                 |

|                                    | $R_{IZ} = \infty$                                                         | 6       |     | kΩ                |

| Input Capacitance                  |                                                                           | 13      |     | рF                |

| Output Impedance                   | Single-ended, either output                                               | 5       |     | Ω                 |

| -3 dB Small Signal Bandwidth       | $V_{OUT} = 0.2 V p-p$                                                     | 130     |     | MHz               |

| Slew Rate                          |                                                                           | 650     |     | V/µs              |

| Input Voltage Noise                | $R_S = 0 \Omega$ , HI or LO gain, $R_{IZ} = \infty$ , $f = 5 \text{ MHz}$ | 0.74    |     | nV/√Hz            |

| Input Current Noise                | $R_{IZ} = \infty$ , HI or LO gain, $f = 5$ MHz                            | 2.5     |     | pA/√Hz            |

| Noise Figure                       | f = 10 MHz, LOP output                                                    |         |     |                   |

| Active Termination Match           | $R_S = R_{IN} = 50 \Omega$                                                | 3.7     |     | dB                |

| Unterminated                       | $R_S = 50 \Omega$ , $R_{IZ} = \infty$                                     | 2.5     |     | dB                |

| Harmonic Distortion @ LOP1 or LOP2 | $V_{OUT} = 0.5 \text{ V p-p, single-ended, f} = 10 \text{ MHz}$           |         |     |                   |

| HD2                                |                                                                           | -56     |     | dBc               |

| HD3                                |                                                                           | -70     |     | dBc               |

| Output Short-Circuit Current       | Pin LON, Pin LOP                                                          | 165     |     | mA                |

| LNA AND VGA CHARACTERISTICS        |                                                                           |         |     |                   |

| –3 dB Small Signal Bandwidth       | $V_{OUT} = 0.2 \text{ V p-p}$                                             |         |     |                   |

| AD8331                             |                                                                           | 120     |     | MHz               |

| AD8332, AD8334                     |                                                                           | 100     |     | MHz               |

| –3 dB Large Signal Bandwidth       | $V_{OUT} = 2 V p-p$                                                       |         |     |                   |

| AD8331                             |                                                                           | 110     |     | MHz               |

| AD8332, AD8334                     |                                                                           | 90      |     | MHz               |

| Slew Rate                          |                                                                           |         |     |                   |

| AD8331                             | LO gain                                                                   | 300     |     | V/µs              |

|                                    | HI gain                                                                   | 1200    |     | V/µs              |

| AD8332, AD8334                     | LO gain                                                                   | 275     |     | V/μs              |

| •                                  | HI gain                                                                   | 1100    |     | V/μs              |

| Input Voltage Noise                | $R_S = 0 \Omega$ , HI or LO gain, $R_{IZ} = \infty$ , $f = 5 \text{ MHz}$ | 0.82    |     | nV/√Hz            |

| Noise Figure                       | V <sub>GAIN</sub> = 1.0 V                                                 |         |     |                   |

| Active Termination Match           | $R_S = R_{IN} = 50 \Omega$ , $f = 10 MHz$ , measured                      | 4.15    |     | dB                |

|                                    | $R_S = R_{IN} = 200 \Omega$ , $f = 5 MHz$ , simulated                     | 2.0     |     | dB                |

| Unterminated                       | $R_S = 50 \Omega$ , $R_{IZ} = \infty$ , $f = 10 MHz$ , measured           | 2.5     |     | dB                |

|                                    | $R_S = 200 \Omega$ , $R_{IZ} = \infty$ , $f = 5 MHz$ , simulated          | 1.0     |     | dB                |

| Output Referred Naiss              | , , , , , , , , , , , , , , , , , , , ,                                   |         |     |                   |

| Output-Referred Noise              | V 05V10 main                                                              | 40      |     | m\// /L1:         |

| AD8331                             | $V_{GAIN} = 0.5 \text{ V, LO gain}$                                       | 48      |     | nV/√Hz            |

| AD0222 AD0224                      | $V_{GAIN} = 0.5 \text{ V, HI gain}$                                       | 178     |     | nV/√Hz            |

| AD8332, AD8334                     | $V_{GAIN} = 0.5 \text{ V, LO gain}$                                       | 40      |     | nV/√Hz            |

|                                    | $V_{GAIN} = 0.5 \text{ V, HI gain}$                                       | 150     |     | nV/√Hz            |

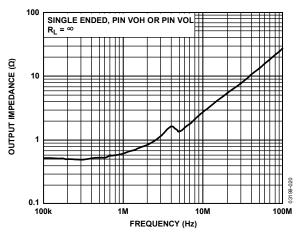

| Output Impedance, Postamplifier    | DC to 1 MHz                                                               | 1       |     | Ω                 |

| Parameter                                     | Conditions                                                                                   | Min  | Тур                     | Max  | Unit1 |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|------|-------------------------|------|-------|

| Output Signal Range, Postamplifier            | $R_L \ge 500 \Omega$ , unclamped, either pin                                                 |      | $V_{\text{CM}}\pm1.125$ |      | V     |

| Differential                                  |                                                                                              |      | 4.5                     |      | V p-p |

| Output Offset Voltage                         |                                                                                              |      |                         |      |       |

| AD8331                                        | Differential, V <sub>GAIN</sub> = 0.5 V                                                      | -50  | ±5                      | +50  | mV    |

|                                               | Common mode                                                                                  | -125 | -25                     | +100 | mV    |

| AD8332, AD8334                                | Differential, $0.05 \text{ V} \leq \text{V}_{GAIN} \leq 1.0 \text{ V}$                       | -20  | ±5                      | +20  | mV    |

|                                               | Common mode                                                                                  | -125 | -25                     | +100 | mV    |

| Output Short-Circuit Current                  |                                                                                              |      | 45                      |      | mA    |

| Harmonic Distortion                           | $V_{GAIN} = 0.5 \text{ V, } V_{OUT} = 1 \text{ V p-p, HI gain}$                              |      |                         |      |       |

| AD8331                                        |                                                                                              |      |                         |      |       |

| HD2                                           | f = 1 MHz                                                                                    |      | -88                     |      | dBc   |

| HD3                                           |                                                                                              |      | -85                     |      | dBc   |

| HD2                                           | f = 10 MHz                                                                                   |      | -68                     |      | dBc   |

| HD3                                           |                                                                                              |      | -65                     |      | dBc   |

| AD8332, AD8334                                |                                                                                              |      |                         |      |       |

| HD2                                           | f = 1 MHz                                                                                    |      | -82                     |      | dBc   |

| HD3                                           |                                                                                              |      | -85                     |      | dBc   |

| HD2                                           | f = 10 MHz                                                                                   |      | -62                     |      | dBc   |

| HD3                                           |                                                                                              |      | -66                     |      | dBc   |

| Input 1 dB Compression Point                  | $V_{GAIN} = 0.25 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 1 \text{ MHz to } 10 \text{ MHz}$ |      | 1                       |      | dBm   |

| Two-Tone Intermodulation Distortion (IMD3)    |                                                                                              |      |                         |      |       |

| AD8331                                        | $V_{GAIN} = 0.72 \text{ V}, V_{OUT} = 1 \text{ V p-p, f} = 1 \text{ MHz}$                    |      | -80                     |      | dBc   |

|                                               | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 10 \text{ MHz}$                    |      | -72                     |      | dBc   |

| AD8332, AD8334                                | $V_{GAIN} = 0.72 \text{ V}, V_{OUT} = 1 \text{ V p-p, f} = 1 \text{ MHz}$                    |      | -78                     |      | dBc   |

|                                               | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 10 \text{ MHz}$                    |      | -74                     |      | dBc   |

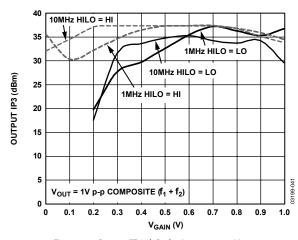

| Output Third-Order Intercept                  |                                                                                              |      |                         |      |       |

| AD8331                                        | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 1 \text{ MHz}$                     |      | 38                      |      | dBm   |

|                                               | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 10 \text{ MHz}$                    |      | 33                      |      | dBm   |

| AD8332, AD8334                                | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 1 \text{ MHz}$                     |      | 35                      |      | dBm   |

|                                               | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 10 \text{ MHz}$                    |      | 32                      |      | dBm   |

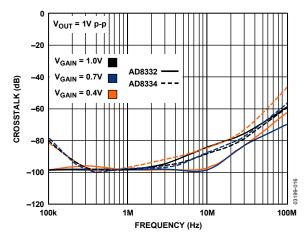

| Channel-to-Channel Crosstalk (AD8332, AD8334) | $V_{GAIN} = 0.5 \text{ V}, V_{OUT} = 1 \text{ V p-p}, f = 1 \text{ MHz}$                     |      | -98                     |      | dB    |

| Overload Recovery                             | $V_{GAIN} = 1.0 \text{ V}, V_{IN} = 50 \text{ mV p-p/1 V p-p, f} = 10 \text{ MHz}$           |      | 5                       |      | ns    |

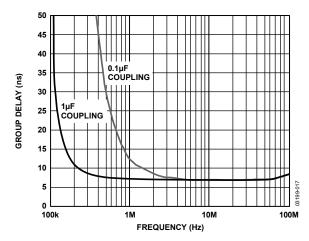

| Group Delay Variation                         | 5 MHz < f < 50 MHz, full gain range                                                          |      | ±2                      |      | ns    |

| ACCURACY                                      |                                                                                              |      |                         |      |       |

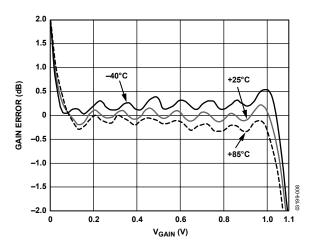

| Absolute Gain Error <sup>2</sup>              | 0.05 V < V <sub>GAIN</sub> < 0.10 V                                                          | -1   | +0.5                    | +2   | dB    |

|                                               | 0.10 V < V <sub>GAIN</sub> < 0.95 V                                                          | -1   | ±0.3                    | +1   | dB    |

|                                               | 0.95 V < V <sub>GAIN</sub> < 1.0 V                                                           | -2   | -1                      | +1   | dB    |

| Gain Law Conformance <sup>3</sup>             | 0.1 V < V <sub>GAIN</sub> < 0.95 V                                                           |      | ±0.2                    |      | dB    |

| Channel-to-Channel Gain Matching              | $0.1 \text{ V} < \text{V}_{\text{GAIN}} < 0.95 \text{ V}$                                    |      | ±0.1                    |      | dB    |

| GAIN CONTROL INTERFACE (Pin GAIN)             |                                                                                              |      |                         |      |       |

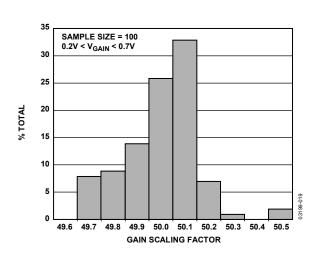

| Gain Scaling Factor                           | 0.10 V < V <sub>GAIN</sub> < 0.95 V                                                          | 48.5 | 50                      | 51.5 | dB/V  |

| Gain Range                                    | LO gain                                                                                      |      | -4.5 to +43.5           |      | dB    |

|                                               | HI gain                                                                                      |      | 7.5 to 55.5             |      | dB    |

| Input Voltage (V <sub>GAIN</sub> ) Range      |                                                                                              |      | 0 to 1.0                |      | V     |

| Input Impedance                               |                                                                                              |      | 10                      |      | МΩ    |

| Response Time                                 | 48 dB gain change to 90% full scale                                                          |      | 500                     |      | ns    |

| COMMON-MODE INTERFACE (PIN VCMx)              |                                                                                              |      |                         |      |       |

| Input Resistance <sup>4</sup>                 | Current limited to ±1 mA                                                                     |      | 30                      |      | Ω     |

| Output CM Offset Voltage                      | $V_{CM} = 2.5 \text{ V}$                                                                     | -125 | -25                     | +100 | mV    |

|                                               |                                                                                              |      |                         |      |       |

| Parameter                                                          | Conditions                                                                | Min  | Тур  | Max  | Unit1 |

|--------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-------|

| ENABLE INTERFACE                                                   |                                                                           |      |      |      |       |

| (PIN ENB, PIN ENBL, PIN ENBV)                                      |                                                                           |      |      |      |       |

| Logic Level to Enable Power                                        |                                                                           | 2.25 |      | 5    | V     |

| Logic Level to Disable Power                                       |                                                                           | 0    |      | 1.0  | V     |

| Input Resistance                                                   | Pin ENB                                                                   |      | 25   |      | kΩ    |

|                                                                    | Pin ENBL                                                                  |      | 40   |      | kΩ    |

|                                                                    | Pin ENBV                                                                  |      | 70   |      | kΩ    |

| Power-Up Response Time                                             | $V_{INH} = 30 \text{ mV p-p}$                                             |      | 300  |      | μs    |

|                                                                    | $V_{INH} = 150 \text{ mV p-p}$                                            |      | 4    |      | ms    |

| HILO GAIN RANGE INTERFACE (PIN HILO)                               |                                                                           |      |      |      |       |

| Logic Level to Select HI Gain Range                                |                                                                           | 2.25 |      | 5    | V     |

| Logic Level to Select LO Gain Range                                |                                                                           | 0    |      | 1.0  | V     |

| Input Resistance                                                   |                                                                           |      | 50   |      | kΩ    |

| OUTPUT CLAMP INTERFACE (PIN RCLMP; HI OR LO GAIN)                  |                                                                           |      |      |      |       |

| Accuracy                                                           |                                                                           |      |      |      |       |

| HILO = LO                                                          | $R_{CLMP} = 2.74 \text{ k}\Omega$ , $V_{OUT} = 1 \text{ V p-p (clamped)}$ |      | ±50  |      | mV    |

| HILO = HI                                                          | $R_{CLMP} = 2.21 \text{ k}\Omega$ , $V_{OUT} = 1 \text{ V p-p (clamped)}$ |      | ±75  |      | mV    |

| MODE INTERFACE (PIN MODE)                                          |                                                                           |      |      |      |       |

| Logic Level for Positive Gain Slope                                |                                                                           | 0    |      | 1.0  | V     |

| Logic Level for Negative Gain Slope                                |                                                                           | 2.25 |      | 5    | V     |

| Input Resistance                                                   |                                                                           |      | 200  |      | kΩ    |

| POWER SUPPLY (PIN VPS1, PIN VPS2,<br>PIN VPSV, PIN VPSL, PIN VPOS) |                                                                           |      |      |      |       |

| Supply Voltage                                                     |                                                                           | 4.5  | 5.0  | 5.5  | V     |

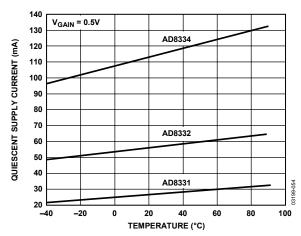

| Quiescent Current per Channel                                      |                                                                           |      |      |      |       |

| AD8331                                                             |                                                                           | 20   | 25   |      | mA    |

| AD8332                                                             |                                                                           | 25   | 27.5 | 32   | mA    |

| AD8334                                                             |                                                                           | 27   | 29.5 | 34   |       |

| Power Dissipation per Channel                                      | No signal                                                                 |      |      |      |       |

| AD8331                                                             |                                                                           |      | 125  |      | mW    |

| AD8332, AD8334                                                     |                                                                           |      | 138  |      | mW    |

| Power-Down Current                                                 | VGA and LNA disabled                                                      |      |      |      |       |

| AD8331                                                             |                                                                           | 50   | 240  | 400  | μΑ    |

| AD8332                                                             |                                                                           | 50   | 300  | 600  | μΑ    |

| AD8334                                                             |                                                                           | 50   | 600  | 1200 | μΑ    |

| LNA Current                                                        |                                                                           |      |      |      |       |

| AD8331 (ENBL)                                                      | Each channel                                                              | 7.5  | 11   | 15   | mA    |

| AD8332, AD8334 (ENBL)                                              | Each channel                                                              | 7.5  | 12   | 15   | mA    |

| VGA Current                                                        |                                                                           |      |      |      |       |

| AD8331 (ENBV)                                                      |                                                                           | 7.5  | 14   | 20   | mA    |

| AD8332, AD8334 (ENBV)                                              |                                                                           | 7.5  | 17   | 20   | mA    |

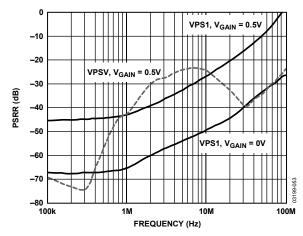

| PSRR                                                               | $V_{GAIN} = 0 \text{ V, } f = 100 \text{ kHz}$                            |      | -68  |      | dB    |

$<sup>^1</sup>$  All dBm values are referred to 50  $\Omega.$   $^2$  The absolute gain refers to the theoretical gain expression in Equation 1.  $^3$  Best-fit to linear-in-dB curve.  $^4$  The current is limited to  $\pm 1$  mA typical.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                               | Rating                  |

|-----------------------------------------|-------------------------|

| Voltage                                 |                         |

| Supply Voltage (VPSn, VPSV, VPSL, VPOS) | 5.5 V                   |

| Input Voltage (INHx)                    | V <sub>S</sub> + 200 mV |

| ENB, ENBL, ENBV, HILO Voltage           | V <sub>s</sub> + 200 mV |

| GAIN Voltage                            | 2.5 V                   |

| Power Dissipation                       |                         |

| AR Package <sup>1</sup> (AD8332)        | 0.96 W                  |

| CP-32 Package (AD8332)                  | 1.97 W                  |

| RQ Package <sup>1</sup> (AD8331)        | 0.78 W                  |

| CP-64 Package (AD8334)                  | 0.91 W                  |

| Temperature                             |                         |

| Operating Temperature Range             | −40°C to +85°C          |

| Storage Temperature Range               | −65°C to +150°C         |

| Lead Temperature (Soldering 60 sec)     | 300°C                   |

| $\theta_{JA}$                           |                         |

| AR Package <sup>1</sup> (AD8332)        | 68°C/W                  |

| CP-32 Package2 <sup>2</sup> (AD8332)    | 33°C/W                  |

| RQ Package <sup>1</sup> (AD8331)        | 83°C/W                  |

| CP-64 Package³ (AD8334)                 | 24.2°C/W                |

<sup>&</sup>lt;sup>1</sup> Four-layer JEDEC board (2S2P).

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2\</sup>mbox{Exposed}$  pad soldered to board, nine thermal vias in pad—JEDEC, four-layer board J-STD-51-9.

<sup>&</sup>lt;sup>3</sup>Exposed pad soldered to board, 25 thermal vias in pad—JEDEC, four-layer board J-STD-51-9.

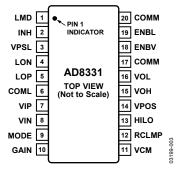

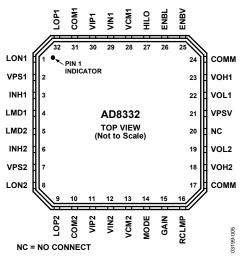

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. 20-Lead QSOP Pin Configuration (AD8331)

Table 3. 20-Lead QSOP Pin Function Description (AD8331)

| Pin No. | Mnemonic | Description                  |  |  |  |

|---------|----------|------------------------------|--|--|--|

| 1       | LMD      | VCM Bias for the LNA         |  |  |  |

| 2       | INH      | LNA Input                    |  |  |  |

| 3       | VPSL     | LNA 5 V Supply               |  |  |  |

| 4       | LON      | LNA Inverting Output         |  |  |  |

| 5       | LOP      | LNA Noninverting Output      |  |  |  |

| 6       | COML     | LNA Ground                   |  |  |  |

| 7       | VIP      | VGA Noninverting Input       |  |  |  |

| 8       | VIN      | VGA Inverting Input          |  |  |  |

| 9       | MODE     | Gain Slope Logic Input       |  |  |  |

| 10      | GAIN     | Gain Control Voltage         |  |  |  |

| 11      | VCM      | Common-Mode Voltage          |  |  |  |

| 12      | RCLMP    | Output Clamping Level        |  |  |  |

| 13      | HILO     | Gain Range Select (HI or LO) |  |  |  |

| 14      | VPOS     | VGA 5 V Supply               |  |  |  |

| 15      | VOH      | Noninverting VGA Output      |  |  |  |

| 16      | VOL      | Inverting VGA Output         |  |  |  |

| 17      | COMM     | VGA Ground                   |  |  |  |

| 18      | ENBV     | VGA Enable                   |  |  |  |

| 19      | ENBL     | LNA Enable                   |  |  |  |

| 20      | COMM     | VGA Ground                   |  |  |  |

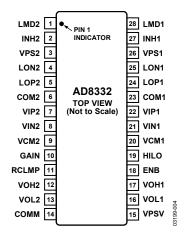

Figure 4. 28-Lead TSSOP Pin Configuration (AD8332)

Figure 5. 32-Lead LFCSP Pin Configuration (AD8332)

Table 4. 28-Lead TSSOP Pin Function Description (AD8332)

| Table 4. 28-Lead TSSOP Pin Function Description (AD8332) |          | Table 5.                         | 32-Lead LFCSP | Pin Function Description (AD833 |                                  |

|----------------------------------------------------------|----------|----------------------------------|---------------|---------------------------------|----------------------------------|

| Pin No.                                                  | Mnemonic | Description                      | Pin No.       | Mnemonic                        | Description                      |

| 1                                                        | LMD2     | VCM Bias for CH2 LNA             | 1             | LON1                            | CH1 LNA Inverting Output         |

| 2                                                        | INH2     | CH2 LNA Input                    | 2             | VPS1                            | CH1 LNA Supply 5 V               |

| 3                                                        | VPS2     | CH2 Supply LNA 5 V               | 3             | INH1                            | CH1 LNA Input                    |

| 4                                                        | LON2     | CH2 LNA Inverting Output         | 4             | LMD1                            | VCM Bias for CH1 LNA             |

| 5                                                        | LOP2     | CH2 LNA Noninverting Output      | 5             | LMD2                            | VCM Bias for CH2 LNA             |

| 6                                                        | COM2     | CH2 LNA Ground                   | 6             | INH2                            | CH2 LNA Input                    |

| 7                                                        | VIP2     | CH2 VGA Noninverting Input       | 7             | VPS2                            | CH2 LNA Supply 5 V               |

| 8                                                        | VIN2     | CH2 VGA Inverting Input          | 8             | LON2                            | CH2 LNA Inverting Output         |

| 9                                                        | VCM2     | CH2 Common-Mode Voltage          | 9             | LOP2                            | CH2 LNA Noninverting Output      |

| 10                                                       | GAIN     | Gain Control Voltage             | 10            | COM2                            | CH2 LNA Ground                   |

| 11                                                       | RCLMP    | Output Clamping Resistor         | 11            | VIP2                            | CH2 VGA Noninverting Input       |

| 12                                                       | VOH2     | CH2 Noninverting VGA Output      | 12            | VIN2                            | CH2 VGA Inverting Input          |

| 13                                                       | VOL2     | CH2 Inverting VGA Output         | 13            | VCM2                            | CH2 Common-Mode Voltage          |

| 14                                                       | COMM     | VGA Ground (Both Channels)       | 14            | MODE                            | Gain Slope Logic Input           |

| 15                                                       | VPSV     | VGA Supply 5 V (Both Channels)   | 15            | GAIN                            | Gain Control Voltage             |

| 16                                                       | VOL1     | CH1 Inverting VGA Output         | 16            | RCLMP                           | Output Clamping Level Input      |

| 17                                                       | VOH1     | CH1 Noninverting VGA Output      | 17            | COMM                            | VGA Ground                       |

| 18                                                       | ENB      | Enable—VGA/LNA                   | 18            | VOH2                            | CH2 Noninverting VGA Output      |

| 19                                                       | HILO     | VGA Gain Range Select (HI or LO) | 19            | VOL2                            | CH2 Inverting VGA Output         |

| 20                                                       | VCM1     | CH1 Common-Mode Voltage          | 20            | NC                              | No Connect                       |

| 21                                                       | VIN1     | CH1 VGA Inverting Input          | 21            | VPSV                            | VGA Supply 5 V                   |

| 22                                                       | VIP1     | CH1 VGA Noninverting Input       | 22            | VOL1                            | CH1 Inverting VGA Output         |

| 23                                                       | COM1     | CH1 LNA Ground                   | 23            | VOH1                            | CH1 Noninverting VGA Output      |

| 24                                                       | LOP1     | CH1 LNA Noninverting Output      | 24            | COMM                            | VGA Ground                       |

| 25                                                       | LON1     | CH1 LNA Inverting Output         | 25            | ENBV                            | VGA Enable                       |

| 26                                                       | VPS1     | CH1 LNA Supply 5 V               | 26            | ENBL                            | LNA Enable                       |

| 27                                                       | INH1     | CH1 LNA Input                    | 27            | HILO                            | VGA Gain Range Select (HI or LO) |

| 28                                                       | LMD1     | VCM Bias for CH1 LNA             | 28            | VCM1                            | CH1 Common-Mode Voltage          |

|                                                          |          |                                  | 29            | VIN1                            | CH1 VGA Inverting Input          |

|                                                          |          |                                  | 30            | VIP1                            | CH1 VGA Noninverting Input       |

|                                                          |          |                                  |               |                                 |                                  |

31 32 COM1

LOP1

CH1 LNA Ground

CH1 LNA Noninverting Output

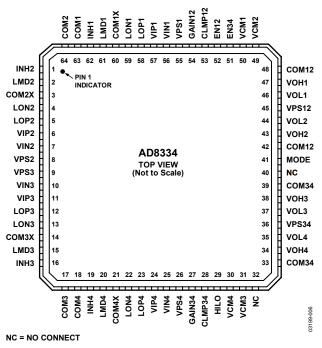

Figure 6. 64-Lead LFCSP Pin Configuration (AD8334)

Table 6. 64-Lead LFCSP Pin Function Description (AD8334)

| Pin No. | Mnemonic | Description                                    |

|---------|----------|------------------------------------------------|

| 1       | INH2     | CH2 LNA Input                                  |

| 2       | LMD2     | VCM Bias for CH2 LNA                           |

| 3       | COM2X    | CH2 LNA Ground Shield                          |

| 4       | LON2     | CH2 LNA Feedback Output (for R <sub>IZ</sub> ) |

| 5       | LOP2     | CH2 LNA Output                                 |

| 6       | VIP2     | CH2 VGA Positive Input                         |

| 7       | VIN2     | CH2 VGA Negative Input                         |

| 8       | VPS2     | CH2 LNA Supply 5 V                             |

| 9       | VPS3     | CH3 LNA Supply 5 V                             |

| 10      | VIN3     | CH3 VGA Negative Input                         |

| 11      | VIP3     | CH3 VGA Positive Input                         |

| 12      | LOP3     | CH3 LNA Positive Output                        |

| 13      | LON3     | CH3 LNA Feedback Output (for R <sub>IZ</sub> ) |

| 14      | COM3X    | CH3 LNA Ground Shield                          |

| 15      | LMD3     | VCM Bias for CH3 LNA                           |

| 16      | INH3     | CH3 LNA Input                                  |

| 17      | COM3     | CH3 LNA Ground                                 |

| 18      | COM4     | CH4 LNA Ground                                 |

| 19      | INH4     | CH4 LNA Input                                  |

| 20      | LMD4     | VCM Bias for CH4 LNA                           |

| 21      | COM4X    | CH4 LNA Ground Shield                          |

| 22      | LON4     | CH4 LNA Feedback Output (for R <sub>IZ</sub> ) |

| 23      | LOP4     | CH4 LNA Positive Output                        |

| 24      | VIP4     | CH4 VGA Positive Input                         |

| 25      | VIN4     | CH4 VGA Negative Input                         |

| 26      | VPS4     | CH4 LNA Supply 5 V                             |

| 27      | GAIN34   | Gain Control Voltage for CH3 and CH4           |

| 28      | CLMP34   | Output Clamping Level Input for CH3 and CH4    |

| Pin No. | Mnemonic | Description                                    |

|---------|----------|------------------------------------------------|

| 29      | HILO     | Gain Select for Postamp 0 dB or 12 dB          |

| 30      | VCM4     | CH4 Common-Mode Voltage—AC Bypass              |

| 31      | VCM3     | CH3 Common-Mode Voltage—AC Bypass              |

| 32      | NC       | No Connect                                     |

| 33      | COM34    | VGA Ground CH3 and CH4                         |

| 34      | VOH4     | CH4 Positive VGA Output                        |

| 35      | VOL4     | CH4 Negative VGA Output                        |

| 36      | VPS34    | VGA Supply 5 V CH3 and CH4                     |

| 37      | VOL3     | CH3 Negative VGA Output                        |

| 38      | VOH3     | CH3 Positive VGA Output                        |

| 39      | COM34    | VGA Ground CH3 and CH4                         |

| 40      | NC       | No Connect                                     |

| 41      | MODE     | Gain Control Slope, Logic Input, 0 = Positive  |

| 42      | COM12    | VGA Ground CH1 and CH2                         |

| 43      | VOH2     | CH2 Positive VGA Output                        |

| 44      | VOL2     | CH2 Negative VGA Output                        |

| 45      | VPS12    | CH2 VGA Supply 5 V CH1 and CH2                 |

| 46      | VOL1     | CH1 Negative VGA Output                        |

| 47      | VOH1     | CH1 Positive VGA Output                        |

| 48      | COM12    | VGA Ground CH1 and CH2                         |

| 49      | VCM2     | CH2 Common-Mode Voltage—AC Bypass              |

| 50      | VCM1     | CH1 Common-Mode Voltage—AC Bypass              |

| 51      | EN34     | Shared LNA/VGA Enable CH3 and CH4              |

| 52      | EN12     | Shared LNA/VGA Enable CH1 and CH2              |

| 53      | CLMP12   | Output Clamping Level Input CH1 and CH2        |

| 54      | GAIN12   | Gain Control Voltage CH1 and CH2               |

| 55      | VPS1     | CH1 LNA Supply 5 V                             |

| 56      | VIN1     | CH1 VGA Negative Input                         |

| 57      | VIP1     | CH1 VGA Positive Input                         |

| 58      | LOP1     | CH1 LNA Positive Output                        |

| 59      | LON1     | CH1 LNA Feedback Output (for R <sub>IZ</sub> ) |

| 60      | COM1X    | CH1 LNA Ground Shield                          |

| 61      | LMD1     | VCM Bias for CH1 LNA                           |

| 62      | INH1     | CH1 LNA Input                                  |

| 63      | COM1     | CH1 LNA Ground                                 |

| 64      | COM2     | CH2 LNA Ground                                 |

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_S = 5$  V,  $R_L = 500$   $\Omega$ ,  $R_S = R_{IN} = 50$   $\Omega$ ,  $R_{IZ} = 280$   $\Omega$ ,  $C_{SH} = 22$  pF, f = 10 MHz,  $R_{CLMP} = \infty$ ,  $C_L = 1$  pF, VCM pin floating, -4.5 dB gain (HILO = LO), and differential output voltage, unless otherwise specified.

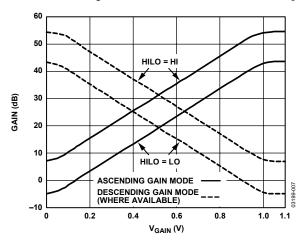

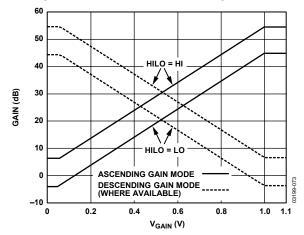

Figure 7. Gain vs. V<sub>GAIN</sub> and MODE (MODE Available on AC Package)

Figure 8. Absolute Gain Error vs. V<sub>GAIN</sub> at Three Temperatures

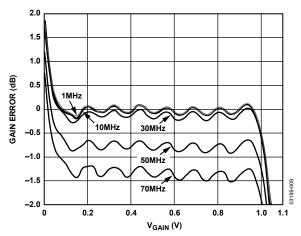

Figure 9. Absolute Gain Error vs. V<sub>GAIN</sub> at Various Frequencies

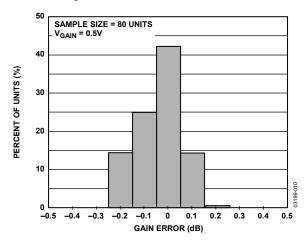

Figure 10. Gain Error Histogram

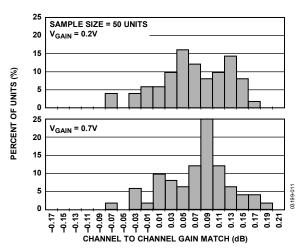

Figure 11. Gain Match Histogram for  $V_{GAIN} = 0.2 V$  and 0.7 V

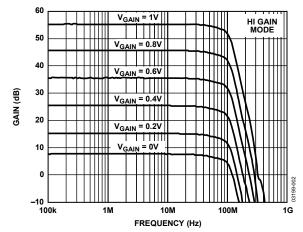

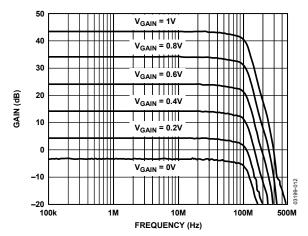

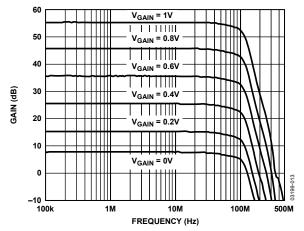

Figure 12. Frequency Response for Various Values of V<sub>GAIN</sub>

Figure 13. Frequency Response for Various Values of  $V_{GAIN}$ , HILO = HI

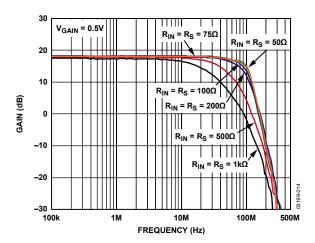

Figure 14. Frequency Response for Various Matched Source Impedances

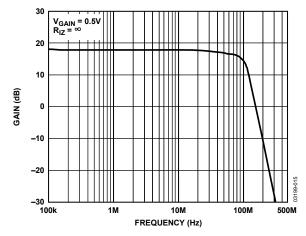

Figure 15. Frequency Response, Unterminated LNA,  $R_S = 50 \Omega$

Figure 16. Channel-to-Channel Crosstalk vs. Frequency for Various Values of V<sub>GAIN</sub>

Figure 17. Group Delay vs. Frequency for Two Values of AC Coupling

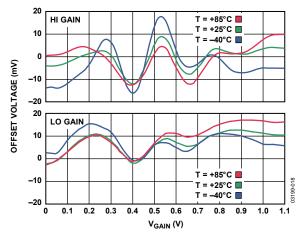

Figure 18. Representative Differential Output Offset Voltage vs.  $V_{GAIN}$  at Three Temperatures

Figure 19. Gain Scaling Factor Histogram

Figure 20. Output Impedance vs. Frequency

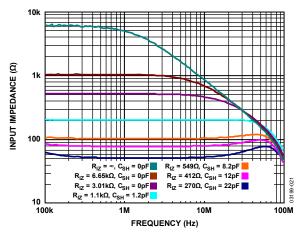

Figure 21. LNA Input Impedance vs. Frequency for Various Values of R<sub>IZ</sub> and C<sub>SH</sub>

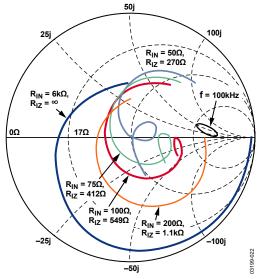

Figure 22. Smith Chart, S11 vs. Frequency, 0.1 MHz to 200 MHz for Various Values of  $R_{\rm IZ}$

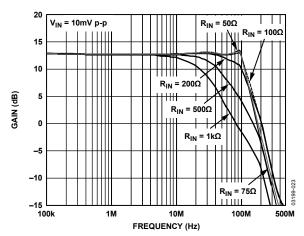

Figure 23. LNA Frequency Response, Single-Ended, for Various Values of  $R_{\text{IN}}$

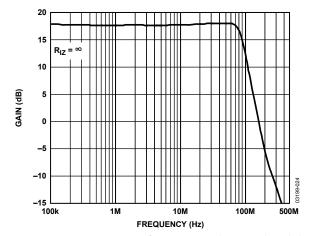

Figure 24. Frequency Response for Unterminated LNA, Single-Ended

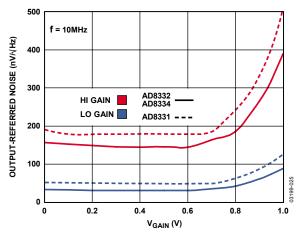

Figure 25. Output-Referred Noise vs.  $V_{\text{GAIN}}$

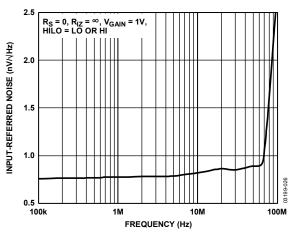

Figure 26. Short-Circuit, Input-Referred Noise vs. Frequency

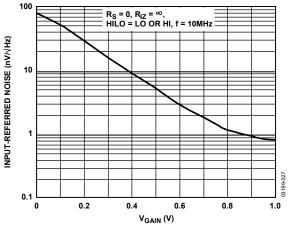

Figure 27. Short-Circuit, Input-Referred Noise vs. V<sub>GAIN</sub>

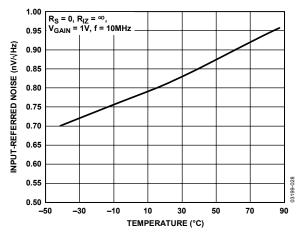

Figure 28. Short-Circuit, Input-Referred Noise vs. Temperature

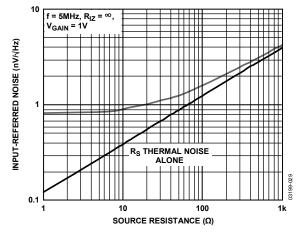

Figure 29. Input-Referred Noise vs. R<sub>S</sub>

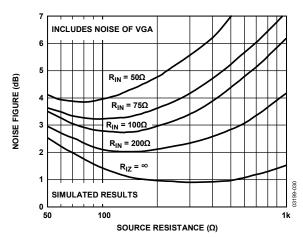

Figure 30. Noise Figure vs. Rs for Various Values of RIN

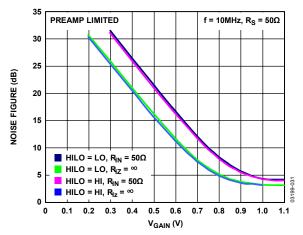

Figure 31. Noise Figure vs. V<sub>GAIN</sub>

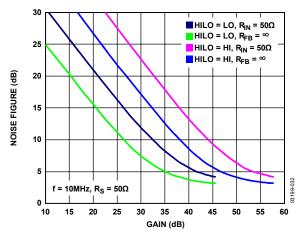

Figure 32. Noise Figure vs. Gain

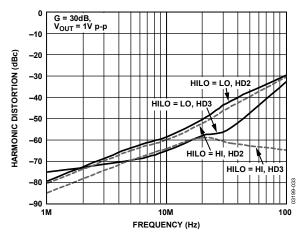

Figure 33. Harmonic Distortion vs. Frequency

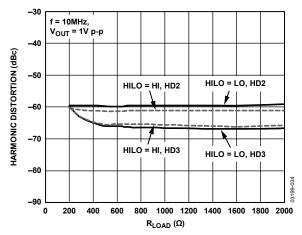

Figure 34. Harmonic Distortion vs. RLOAD

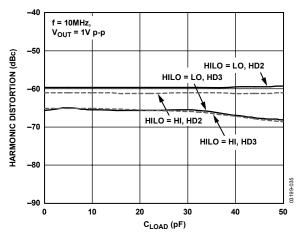

Figure 35. Harmonic Distortion vs. CLOAD

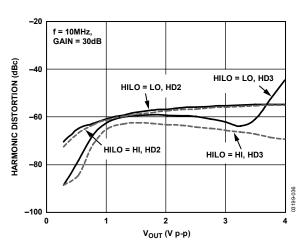

Figure 36. Harmonic Distortion vs. Differential Output Voltage

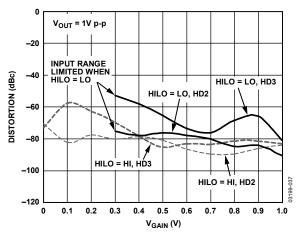

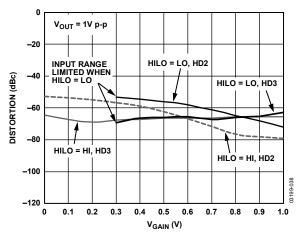

Figure 37. Harmonic Distortion vs.  $V_{GAIN}$ , f = 1 MHz

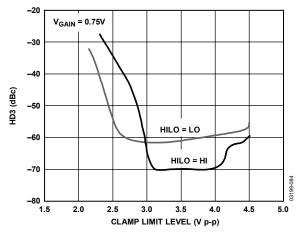

Figure 38. Harmonic Distortion vs.  $V_{GAIN}$ , f = 10 MHz

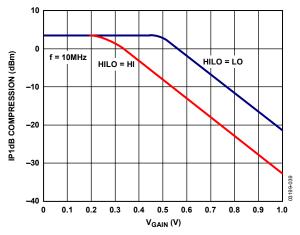

Figure 39. IP1dB Compression vs.  $V_{GAIN}$

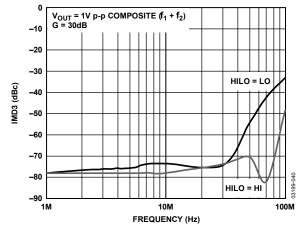

Figure 40. IMD3 vs. Frequency

Figure 41. Output Third-Order Intercept vs. V<sub>GAIN</sub>

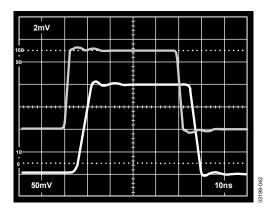

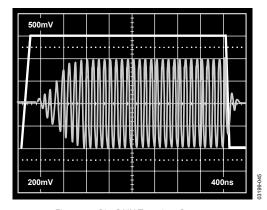

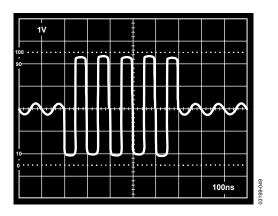

Figure 42. Small Signal Pulse Response,  $G = 30 \, dB$ , Top: Input, Bottom: Output Voltage, HILO = HI or LO

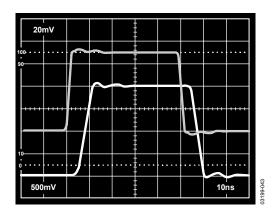

Figure 43. Large Signal Pulse Response,  $G = 30 \, dB$ , HILO = HI or LO, Top: Input, Bottom: Output Voltage

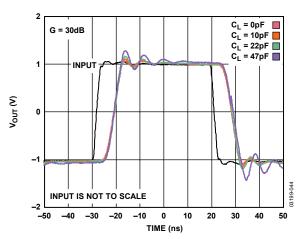

Figure 44. Large Signal Pulse Response for Various Capacitive Loads,  $C_L = 0$  pF, 10 pF, 20 pF, 50 pF

Figure 45. Pin GAIN Transient Response, Top: V<sub>GAIN</sub>, Bottom: Output Voltage

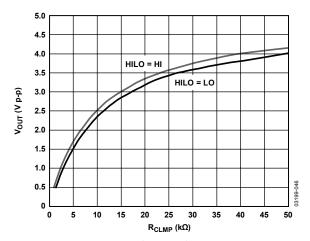

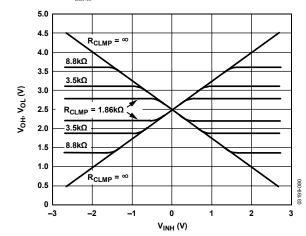

Figure 46. Clamp Level vs. RCLMP

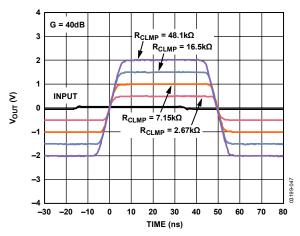

Figure 47. Clamp Level Pulse Response for Four Values of  $R_{\text{CLMP}}$

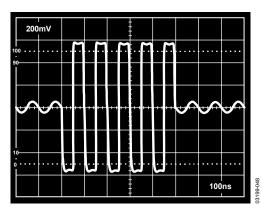

Figure 48. LNA Overdrive Recovery,  $V_{\rm INH}$  0.05 V p-p to 1 V p-p Burst,  $V_{\rm GAIN} = 0.27$  V VGA Output Shown

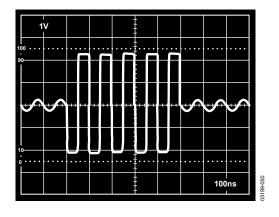

Figure 49. VGA Overdrive Recovery,  $V_{\it INH}$  4 mV p-p to 70 mV p-p Burst,  $V_{\it GAIN}$  = 1 V VGA Output Shown Attenuated by 24 dB

Figure 50. VGA Overdrive Recovery,  $V_{\rm INH}$  4 mV p-p to 275 mV p-p Burst,  $V_{\rm GAIN}=1$  V VGA Output Shown Attenuated by 24 dB

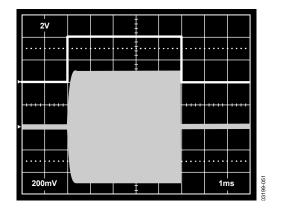

Figure 51. Enable Response, Top:  $V_{ENB}$ , Bottom:  $V_{OUT}$ ,  $V_{INH} = 30 \text{ mV p-p}$

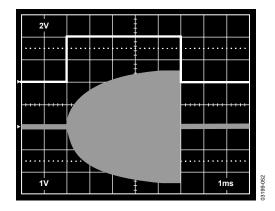

Figure 52. Enable Response, Large Signal, Top:  $V_{ENB}$ , Bottom:  $V_{OUT}$ ,  $V_{INH} = 150$  mV p-p

Figure 53. PSRR vs. Frequency (No Bypass Capacitor)

Figure 54. Quiescent Supply Current vs. Temperature

### **TEST CIRCUITS**

#### **MEASUREMENT CONSIDERATIONS**

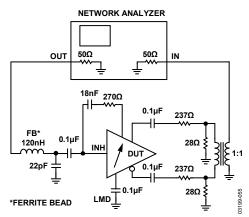

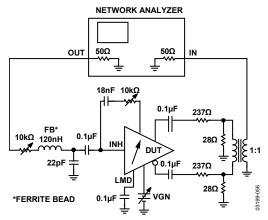

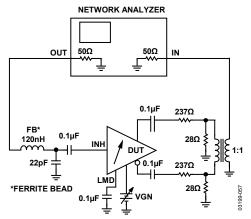

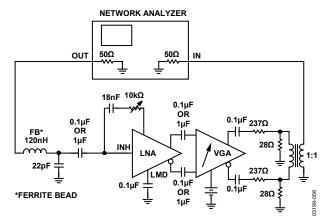

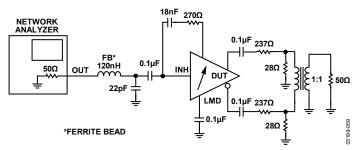

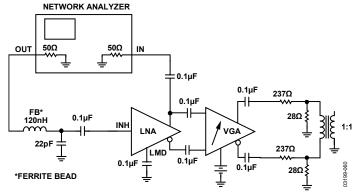

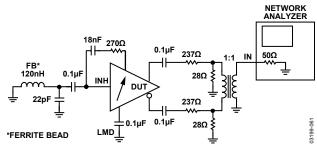

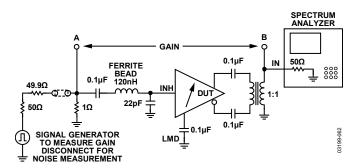

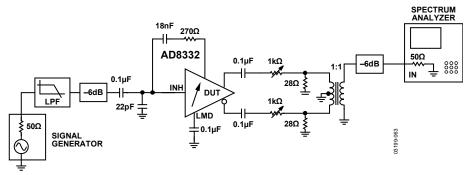

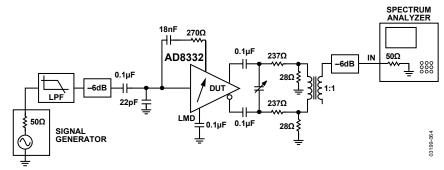

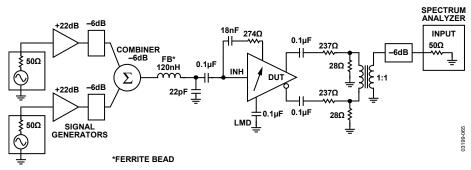

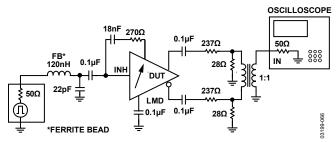

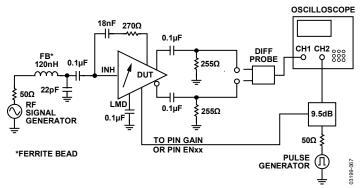

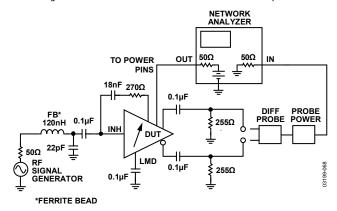

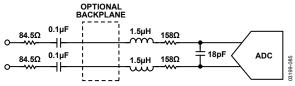

Figure 55 through Figure 68 show typical measurement configurations and proper interface values for measurements with 50  $\Omega$  conditions.

Short-circuit input noise measurements are made as shown in Figure 62. The input-referred noise level is determined by

dividing the output noise by the numerical gain between Point A and Point B and accounting for the noise floor of the spectrum analyzer. The gain should be measured at each frequency of interest and with low signal levels because a 50  $\Omega$  load is driven directly. The generator is removed when noise measurements are made.

Figure 55. Test Circuit—Gain and Bandwidth Measurements

Figure 56. Test Circuit—Frequency Response for Various Matched Source Impedances

Figure 57. Test Circuit—Frequency Response for Unterminated LNA,  $R_S = 50 \Omega$

Figure 58. Test Circuit—Group Delay vs. Frequency for Two Values of AC Coupling

Figure 59. Test Circuit—LNA Input Impedance vs. Frequency in Standard and Smith Chart (S11) Formats

Figure 60. Test Circuit—Frequency Response for Unterminated LNA, Single-Ended

Figure 61. Test Circuit—Short-Circuit, Input-Referred Noise

Figure 62. Test Circuit—Noise Figure

Figure 63. Test Circuit—Harmonic Distortion vs. Load Resistance

Figure 64. Test Circuit—Harmonic Distortion vs. Load Capacitance

Figure 65.Test Circuit—IMD3 vs. Frequency

Figure 66. Test Circuit—Pulse Response Measurements

Figure 67. Test Circuit—Gain and Enable Transient Response

Figure 68. Test Circuit—PSRR vs. Frequency

### THEORY OF OPERATION

#### **OVERVIEW**

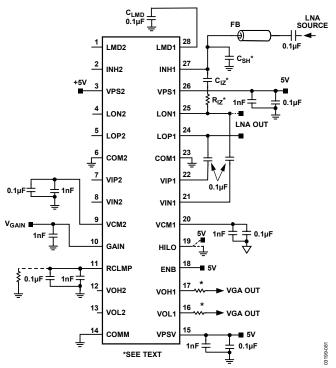

The AD8331/AD8332/AD8334 operate in the same way. Figure 69, Figure 70, and Figure 71 are functional block diagrams of the three devices

Figure 69. AD8331 Functional Block Diagram

Figure 70. AD8332 Functional Block Diagram

Figure 71. AD8334 Functional Block Diagram

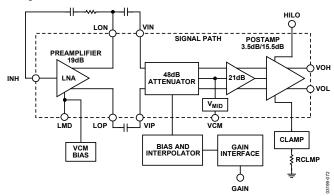

Each channel contains an LNA that provides user-adjustable input impedance termination, a differential X-AMP VGA, and a programmable gain postamp with adjustable output voltage limiting. Figure 72 shows a simplified block diagram with external components.

Figure 72. Simplified Block Diagram

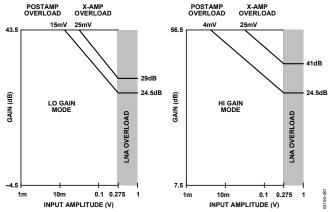

The linear-in-dB gain-control interface is trimmed for slope and absolute accuracy. The gain range is 48 dB, extending from -4.5 dB to +43.5 dB in LO gain and +7.5 dB to +55.5 dB in HI gain mode. The slope of the gain control interface is 50 dB/V, and the gain control range is 40 mV to 1 V. Equation 1 and Equation 2 are the expressions for gain.

$$GAIN (dB) = 50 (dB/V) \times V_{GAIN} - 6.5 dB, (HILO = LO)$$

(1)

or

$$GAIN (dB) = 50 (dB/V) \times V_{GAIN} + 5.5 dB, (HILO = HI)$$

(2)

The ideal gain characteristics are shown in Figure 73.

Figure 73. Ideal Gain Control Characteristics

The gain slope is negative with MODE pulled high (where available), as follows:

$$GAIN (dB) = -50 (dB/V) \times V_{GAIN} + 45.5 dB, (HILO = LO)$$

(3)

or

$$GAIN (dB) = -50 (dB/V) \times V_{GAIN} + 57.5 dB, (HILO = HI)$$

(4)

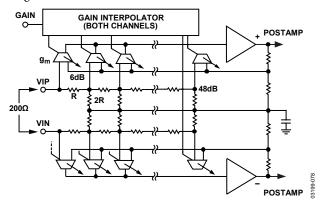

The LNA converts a single-ended input to a differential output with a voltage gain of 19 dB. If only one output is used, the gain is 13 dB. The inverting output is used for active input impedance termination. Each of the LNA outputs is capacitively coupled to a VGA input. The VGA consists of an attenuator with a range of 48 dB followed by an amplifier with 21 dB of gain for a net gain range of –27 dB to +21 dB. The X-AMP gain-interpolation technique results in low gain error and uniform bandwidth, and differential signal paths minimize distortion.

The final stage is a logic programmable amplifier with gains of 3.5 dB or 15.5 dB. The LO and HI gain modes are optimized for 12-bit and 10-bit ADC applications, in terms of output-referred noise and absolute gain range. Output voltage limiting can be programmed by the user.

#### **LOW NOISE AMPLIFIER (LNA)**

Good noise performance in the AD8331/AD8332/AD8334 relies on a proprietary ultralow noise preamplifier at the beginning of the signal chain, which minimizes the noise contribution in the following VGA. Active impedance control optimizes noise performance for applications that benefit from input matching.

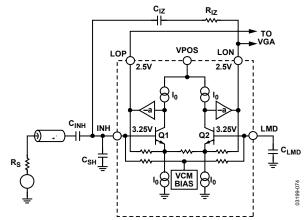

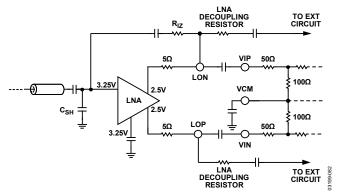

A simplified schematic of the LNA is shown in Figure 74. INH is capacitively coupled to the source. A bias generator establishes dc input bias voltages of 3.25 V and centers the output common-mode levels at 2.5 V. A capacitor  $C_{LMD}$  (can be the same value as the input coupling capacitor  $C_{INH}$ ) is connected from the LMD pin to ground.

Figure 74. Simplified LNA Schematic

The LNA supports differential output voltages as high as 5 V p-p, with positive and negative excursions of  $\pm 1.25$  V, about a common-mode voltage of 2.5 V. Because the differential gain magnitude is 9, the maximum input signal before saturation is  $\pm 275$  mV or  $\pm 550$  mV p-p. Overload protection ensures quick recovery time from large input voltages. Because the inputs are capacitively coupled to a bias voltage near midsupply, very large inputs can be handled without interacting with the ESD protection.

Low value feedback resistors and the current-driving capability of the output stage allow the LNA to achieve a low input-referred voltage noise of  $0.74~\text{nV}/\sqrt{\text{Hz}}$ . This is achieved with a current consumption of only 11 mA per channel (55 mW). On-chip resistor matching results in precise single-ended gains of  $4.5\times$  (9× differential), critical for accurate impedance control. The use of a fully differential topology and negative feedback minimizes distortion. Low HD2 is particularly important in second harmonic ultrasound imaging applications. Differential signaling enables smaller swings at each output, further reducing third-order distortion.

#### **Active Impedance Matching**

The LNA supports active impedance matching through an external shunt feedback resistor from Pin LON to Pin INH. The input resistance,  $R_{\rm IN}$ , is given in Equation 5, where A is the single-ended gain of 4.5, and 6 k $\Omega$  is the unterminated input impedance.

$$R_{IN} = \frac{R_{IZ}}{1+A} \parallel 6 \text{ k}\Omega = \frac{6 \text{ k}\Omega \times R_{IZ}}{33 \text{ k}\Omega + R_{IZ}}$$

(5)

$C_{IZ}$  is needed in series with  $R_{IZ}$  because the dc levels at Pin LON and Pin INH are unequal. Expressions for choosing  $R_{IZ}$  in terms of  $R_{IN}$  and for choosing  $C_{IZ}$  are found in the Applications Information section.  $C_{SH}$  and the ferrite bead enhance stability at higher frequencies, where the loop gain is diminished, and prevent peaking. Frequency response plots of the LNA are shown in Figure 23 and Figure 24. The bandwidth is approximately 130 MHz for matched input impedances of 50  $\Omega$  to 200  $\Omega$  and declines at higher source impedances. The unterminated bandwidth (when  $R_{IZ} = \infty$ ) is approximately 80 MHz.

Each output can drive external loads as low as 100  $\Omega$  in addition to the 100  $\Omega$  input impedance of the VGA (200  $\Omega$  differential). Capacitive loading up to 10 pF is permissible. All loads should be ac-coupled. Typically, Pin LOP output is used as a single-ended driver for auxiliary circuits, such as those used for Doppler ultrasound imaging. Pin LON drives  $R_{\rm IZ}$ . Alternatively, a differential external circuit can be driven from the two outputs in addition to the active feedback termination. In both cases, important stability considerations discussed in the Applications Information section should be carefully observed.

The impedance at each LNA output is 5  $\Omega.$  A 0.4 dB reduction in open-circuit gain results when driving the VGA, and a 0.8 dB reduction results with an additional 100  $\Omega$  load at the output. The differential gain of the LNA is 6 dB higher. If the load is less than 200  $\Omega$  on either side, a compensating load is recommended on the opposite output.

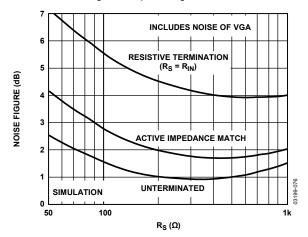

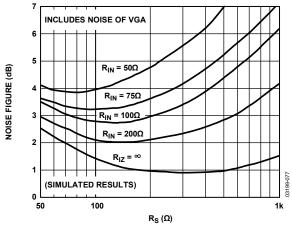

#### **LNA Noise**

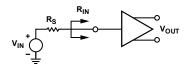

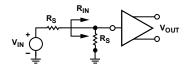

The input-referred voltage noise sets an important limit on system performance. The short-circuit input voltage noise of the LNA is 0.74 nV/ $\sqrt{\text{Hz}}$  or 0.82 nV/ $\sqrt{\text{Hz}}$  (at maximum gain), including the VGA noise. The open-circuit current noise is 2.5 pA/ $\sqrt{\text{Hz}}$ . These measurements, taken without a feedback resistor, provide the basis for calculating the input noise and noise figure performance of the configurations in Figure 75. Figure 76 and Figure 77 show simulations extracted from these results and the 4.1 dB noise figure (NF) measurement with the input actively matched to a 50  $\Omega$  source. Unterminated (R<sub>IZ</sub> = ∞) operation exhibits the lowest equivalent input noise and noise figure. Figure 76 shows the noise figure vs. source resistance, rising at low Rs, where the LNA voltage noise is large compared to the source noise, and again at high Rs due to current noise. The VGA input-referred voltage noise of 2.7  $nV/\sqrt{Hz}$  is included in all of the curves.

#### UNTERMINATED

#### RESISTIVE TERMINATION

ACTIVE IMPEDANCE MATCH - R<sub>S</sub> = R<sub>IN</sub>

$R_{IN} \cong \frac{R_{IZ}}{1+4.5}$

Figure 75. Input Configurations

Figure 76. Noise Figure vs. R<sub>S</sub> for Resistive, Active Match, and Unterminated Inputs

Figure 77. Noise Figure vs. Rs for Various Fixed Values of R<sub>IN</sub>, Actively Matched

The primary purpose of input impedance matching is to improve the system transient response. With resistive termination, the input noise increases due to the thermal noise of the matching resistor and the increased contribution of the LNA input voltage noise generator. With active impedance matching, however, the contributions of both are smaller than they would be for resistive termination by a factor of  $1/(1 + LNA\ Gain)$ . Figure 76 shows their relative NF performance. In this graph, the input impedance is swept with Rs to preserve the match at each point. The noise figures for a source impedance of 50  $\Omega$  are 7.1 dB, 4.1 dB, and 2.5 dB, respectively, for the resistive, active, and unterminated configurations. The noise figures for 200  $\Omega$  are 4.6 dB, 2.0 dB, and 1.0 dB, respectively.

Figure 77 is a plot of NF vs.  $R_S$  for various values of  $R_{IN}$ , which is helpful for design purposes. The plateau in the NF for actively matched inputs mitigates source impedance variations. For comparison purposes, a preamp with a gain of 19 dB and noise spectral density of  $1.0~\text{nV/}\sqrt{\text{Hz}}$ , combined with a VGA with  $3.75~\text{nV/}\sqrt{\text{Hz}}$ , yields a noise figure degradation of approximately 1.5~dB (for most input impedances), significantly worse than the AD8331/AD8332/AD8334 performance.

The equivalent input noise of the LNA is the same for single-ended and differential output applications. The LNA noise figure improves to 3.5 dB at 50  $\Omega$  without VGA noise, but this is exclusive of noise contributions from other external circuits connected to LOP. A series output resistor is usually recommended for stability purposes when driving external circuits on a separate board (see the Applications Information section). In low noise applications, a ferrite bead is even more desirable.

#### **VARIABLE GAIN AMPLIFIER**

The differential X-AMP VGA provides precise input attenuation and interpolation. It has a low input-referred noise of 2.7~nV/VHz and excellent gain linearity. A simplified block diagram is shown in Figure 78.

Figure 78. Simplified VGA Schematic

#### X-AMP VGA

The input of the VGA is a differential R-2R ladder attenuator network with 6 dB steps per stage and a net input impedance of 200  $\Omega$  differential. The ladder is driven by a fully differential input signal from the LNA and is not intended for single-ended operation. LNA outputs are ac-coupled to reduce offset and isolate their common-mode voltage. The VGA inputs are biased through the center tap connection of the ladder to VCM, which is typically set to 2.5 V and is bypassed externally to provide a clean ac ground.

The signal level at successive stages in the input attenuator falls from 0 dB to -48 dB in 6 dB steps. The input stages of the X-AMP are distributed along the ladder, and a biasing interpolator, controlled by the gain interface, determines the input tap point. With overlapping bias currents, signals from successive taps merge to provide a smooth attenuation range from 0 dB to -48 dB. This circuit technique results in excellent linear-in-dB gain law conformance and low distortion levels and deviates  $\pm 0.2$  dB or less from the ideal. The gain slope is monotonic with respect to the control voltage and is stable with variations in process, temperature, and supply.

The X-AMP inputs are part of a gain-of-12 feedback amplifier that completes the VGA. Its bandwidth is 150 MHz. The input stage is designed to reduce feedthrough to the output and to ensure excellent frequency response uniformity across gain setting (see Figure 12 and Figure 13).

#### **Gain Control**

Position along the VGA attenuator is controlled by a single-ended analog control voltage,  $V_{\rm GAIN}$ , with an input range of 40 mV to 1.0 V. The gain control scaling is trimmed to a slope of 50 dB/V (20 mV/dB). Values of  $V_{\rm GAIN}$  beyond the control range saturate to minimum or maximum gain values. Both channels of the AD8332 are controlled from a single gain interface to preserve matching. Gain can be calculated using Equation 1 and Equation 2.

Gain accuracy is very good because both the scaling factor and absolute gain are factory trimmed. The overall accuracy relative to the theoretical gain expression is  $\pm 1$  dB for variations in temperature, process, supply voltage, interpolator gain ripple, trim errors, and tester limits. The gain error relative to a best-fit line for a given set of conditions is typically  $\pm 0.2$  dB. Gain matching between channels is better than 0.1 dB (Figure 11 shows gain errors in the center of the control range). When  $V_{\rm GAIN} < 0.1$  or > 0.95, gain errors are slightly greater.

The gain slope can be inverted, as shown in Figure 73 (except for the AD8332 AR models). The gain drops with a slope of -50 dB/V across the gain control range from maximum to minimum gain. This slope is useful in applications such as automatic gain control, where the control voltage is proportional to the measured output signal amplitude. The inverse gain mode is selected by setting the MODE pin to HI gain mode.

Gain control response time is less than 750 ns to settle within 10% of the final value for a change from minimum to maximum gain.

#### **VGA** Noise

In a typical application, a VGA compresses a wide dynamic range input signal to within the input span of an ADC. While the input-referred noise of the LNA limits the minimum resolvable input signal, the output-referred noise, which depends primarily on the VGA, limits the maximum instantaneous dynamic range that can be processed at any one particular gain control voltage. This limit is set in accordance with the quantization noise floor of the ADC.

Output and input-referred noise as a function of  $V_{\text{GAIN}}$  are plotted in Figure 25 and Figure 27 for the short-circuited input conditions. The input noise voltage is simply equal to the output noise divided by the measured gain at each point in the control range.

The output-referred noise is flat over most of the gain range because it is dominated by the fixed output-referred noise of the VGA. Values are  $48 \text{ nV}/\sqrt{\text{Hz}}$  in LO gain mode and  $178 \text{ nV}/\sqrt{\text{Hz}}$  in HI gain mode. At the high end of the gain control range, the noise of the LNA and the noise of the source prevail. The input-referred noise reaches its minimum value near the maximum gain control voltage, where the input-referred contribution of the VGA becomes very small.

At lower gains, the input-referred noise, and thus noise figure, increases as the gain decreases. The instantaneous dynamic range of the system is not lost, however, because the input capacity increases with it. The contribution of the ADC noise floor has the same dependence as well. The important relationship is the magnitude of the VGA output noise floor relative to that of the ADC.

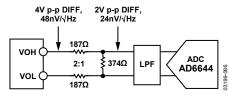

With its low output-referred noise levels, these devices ideally drive low voltage ADCs. The converter noise floor drops 12 dB for every two bits of resolution and drops at lower input full-scale voltages and higher sampling rates. ADC quantization noise is discussed in the Applications Information section.

The preceding noise performance discussion applies to a differential VGA output signal. Although the LNA noise performance is the same in single-ended and differential applications, the VGA performance is not. The noise of the VGA is significantly higher in single-ended usage because the contribution of its bias noise is designed to cancel in the differential signal. A transformer can be used with single-ended applications when low noise is desired.

Gain control noise is a concern in very low noise applications. Thermal noise in the gain control interface can modulate the channel gain. The resultant noise is proportional to the output signal level and usually only evident when a large signal is present. Its effect is observable only in LO gain mode where the noise floor is substantially lower. The gain interface includes an on-chip noise filter, which reduces this effect significantly at frequencies above 5 MHz. Care should be taken to minimize noise impinging at the GAIN input. An external RC filter can be used to remove  $V_{\text{GAIN}}$  source noise. The filter bandwidth should be sufficient to accommodate the desired control bandwidth.

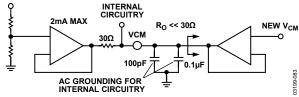

#### **Common-Mode Biasing**

An internal bias network connected to a midsupply voltage establishes common-mode voltages in the VGA and postamp. An externally bypassed buffer maintains the voltage. The bypass capacitors form an important ac ground connection because the VCM network makes a number of important connections internally, including the center tap of the VGA differential input attenuator, the feedback network of the VGA fixed gain amplifier, and the feedback network of the postamp in both gain settings. For best results, use a 1 nF capacitor and a 0.1  $\mu F$  capacitor in parallel, with the 1 nF capacitor nearest to the VCM pin. Separate VCM pins are provided for each channel. For dc coupling to a 3 V ADC, the output common-mode voltage is adjusted to 1.5 V by biasing the VCM pin.

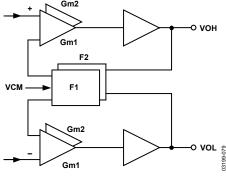

#### **POSTAMPLIFIER**

The final stage has a selectable gain of 3.5 dB ( $\times$ 1.5) or 15.5 dB ( $\times$ 6), set by the HILO logic pin. Figure 79 is a simplified block diagram.

Figure 79. Postamplifier Block Diagram

Separate feedback attenuators implement the two gain settings. These are selected in conjunction with an appropriately scaled input stage to maintain a constant 3 dB bandwidth between the two gain modes (~150 MHz). The slew rate is 1200 V/ $\mu$ s in HI gain mode and 300 V/ $\mu$ s in LO gain mode. The feedback networks for HI and LO gain modes are factory trimmed to adjust the absolute gains of each channel.

#### Noise